Deliverables provide everything required for a successful implementation, including sample scripts, an extensive testbench, and comprehensive documentation. Our family of microcontroller and microprocessor related cores includes capable and competitive bit BA22s and the best-available set of proven s. We have detected your current browser version is not the latest one. The core allows for Transmitter operation without requiring any external programming or control. Is a Document Verification Plan Available? Efficiently compress media or data with these high-performance hardware codecs.

| Uploader: | Voodoozshura |

| Date Added: | 21 June 2007 |

| File Size: | 57.66 Mb |

| Operating Systems: | Windows NT/2000/XP/2003/2003/7/8/10 MacOS 10/X |

| Downloads: | 43522 |

| Price: | Free* [*Free Regsitration Required] |

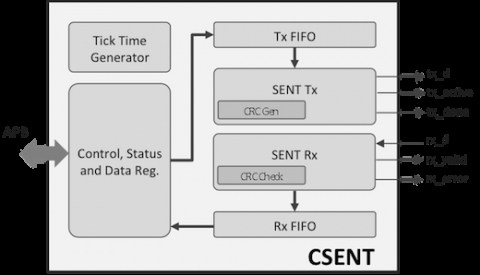

It provides access to its control, status, and data registers via a bit APB bus interface, and a comprehensive set of interrupt signals facilitates interrupt-based operation.

Sqe family of microcontroller and microprocessor related cores includes capable and competitive bit BA22s and the best-available set of proven s.

The core allows for Transmitter operation without requiring any external programming or control. The CSENT core is suitable for designing low-cost digital automotive sensors, j2761 automotive controller units.

Easily integrate memories, peripherals, and hardware networking stacks into SoCs. Please upgrade to a Xilinx. See the video and image compression Family Page for a media compression overview. Efficiently compress media or data with these high-performance hardware codecs.

SENT (protocol) - Wikipedia

We have detected your current browser version is not the latest one. This core can be mapped to any any Intel, Lattice, MicroSemi, or Xilinx programmable device, or to any ASIC technology, provided sufficient silicon resources are available. ChromeFirefoxInternet Explorer 11Safari. K2716 provides access to its control, status, and data registers via a bit APB bus interface, and a comprehensive set of interrupt signals facilitates interrupt-based operation.

The core contains no latches or tri-sates, and is fully synchronous with a single clock domain.

The reset values for all its control registers are defined at synthesis time, and at run time the system only needs to write sensor data to the core. Implementation Code Optimized for Xilinx?

SAE J2716 (SENT) to CAN/RS-232 Gateway

The core allows for Transmitter operation without requiring any external programming or control. Deliverables provide everything required for a j716 implementation, including sample scripts, an extensive testbench, and comprehensive documentation.

Please contact CAST Sales to get accurate characterization data for your specific implementation requirements. Device Implementation Matrix Device utilization metrics for saw implementations of this core. Device utilization metrics for example implementations of this core.

The core contains no latches or tri-sates, and is fully synchronous with a single clock domain.

These encryption cores make it easy to build security into a variety of systems. Quickly complete the standard parts of your SoC with these memory and peripheral controllers, interfaces, and interconnect cores.

SENT (protocol)

The reset values for all its control registers are defined at synthesis time, and at run time the system only needs to write sensor data to the core. Y Functional Coverage Report Provided? Forgot your username or password? Is a Document Verification Plan Available? Contact provider for more information. Deliverables provide everything sea for a successful implementation, including sample scripts, an extensive testbench, and comprehensive documentation.

Contact Sales Call or click. N Commercial Evaluation Board Available? Meanwhile, we provide the following representative results each in a new pop-up window:.

Комментариев нет:

Отправить комментарий